Ajouter à mes favoris

Voir la traduction automatique

Ceci est une traduction automatique. Pour voir le texte original en anglais

cliquez ici

#Tendances produits

{{{sourceTextContent.title}}}

L'adapteur de PCIe2RasPI accueille les cartes d'entrée-sortie de la framboise pi sur une mini fente de PCIe.

{{{sourceTextContent.subTitle}}}

Rome, entreprise de GEB livre l'adapteur de PCIe2RasPI faisant capable les cartes mères incorporées de PCIE pour accueillir tous les panneaux d'entrée-sortie de framboise

{{{sourceTextContent.description}}}

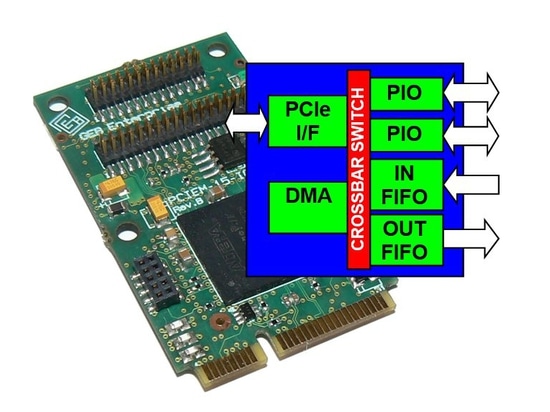

L'adapteur de PCIe2RasPI, relié sur le mini connecteur d'entrée-sortie de PCIe et les FPGA programmables font disponible la même fonction de goupilles disponible sur la framboise et plus…. les goupilles disponibles de frais supplémentaires peuvent être utilisées pour donner la fonctionnalité et la vitesse qui ne peuvent pas être atteintes avec l'exécution de logiciel sur l'unité centrale de traitement de framboise.

Vraiment quand une mini carte de PCIE Fpga a été reliée à une carte mère incorporée de PC, elle ajoute des possibilités élevées programmables d'entrée-sortie et de DSP de largeur de bande de FPGA à un coût bas, lui faisant l'idéal pour des équipements dans beaucoup de champs d'application, tels qu'électromédical, l'automation, les joueurs de données et les enregistreurs et ainsi de suite.

Beaucoup d'applications peuvent être développées utilisant les outils d'outil de FEWE (éditeur Web facile de Fpga) GEB librement qui viendra bientôt. Il permet aux utilisateurs d'adapter aux besoins du client pour posséder l'application à partir d'un certain calibre créé par GEB utilisant un web browser, sans n'importe quel autre outil.

Également des calibres définis pour l'utilisateur peuvent être obtenus utilisant le calibre relatif

Le contenu de Fpga peut être développé également utilisant les outils traditionnels de Quartus ou demander une personnalisation à l'entreprise de GEB. Les kits relatifs de développement font disponible tous de ce que vous avez besoin pour développer la conception de Fpga sous Altera QSYS et le programme d'application utilisant les conducteurs fournis de Microsoft Windows ou de Linux.

Le PCIEM-15-IO accueille un cyclone IV GX EP4CGX30BF14C6N FPGA et deux connecteurs d'entrée-sortie qui mettent en évidence 53 bornes conformes de l'entrée-sortie FPGA de LVTTL et également signal d'Altera de 3 horloges qui peut être employé pour connecter des applications synchrones.

Le FPGA a une interface de cible de PCI Express PCIe x1 GEN1, permettant au PC de profiter pleinement des goupilles d'entrée-sortie de FPGA. Les goupilles d'entrée-sortie peuvent également être commandées par un contrôleur DMA de haute performance, capable transférer jusqu'à 250 Moctets/sec une fois utilisées dans duplex